Dispositifs mobiles Samsung à utiliser plus puissants et efficaces puissance des processeurs 14nm

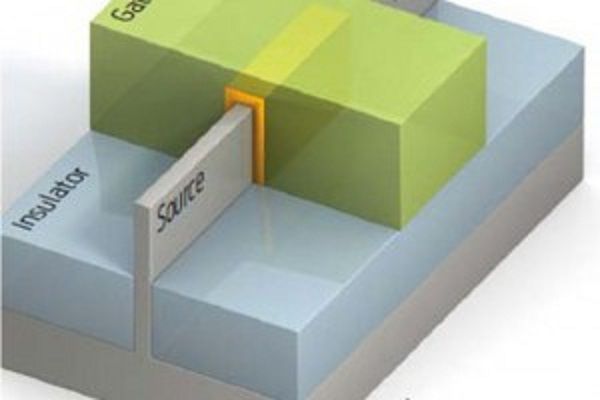

Samsung a annoncé un processeur Cortex-A7 nouvelle ARM qui dispose de la technologie 14nm pour ses futurs appareils. La puissante nouvelle puce apporte de nombreuses améliorations de performances sur les puces précédentes. Le nouveau design Samsung a présenté est comparé avec Tri-Gate d'Intel qui se trouve dans les chipsets Ivy Bridge et est considéré comme très bon par beaucoup.

Le nouveau design offre non seulement sensiblement plus de puissance mais aussi une faible fuite. La nouvelle puce a été présenté comme un résultat de la collaboration entre Samsung ARM et Synopsys. La nouvelle puce a été testé avec succès sur 14nm FinFET la technologie de processus. Il a été révélé dans un communiqué de presse que la société a signé avec ARM pour les IP de 14nm et les bibliothèques physiques.

Peut-être la caractéristique la plus importante et notable de cette nouvelle puce produite par Samsung et ses partenaires est qu'il consomme moins d'énergie et offre plus de traitement du muscle en même temps. Selon les entreprises, leurs nouvelles puces 14nm fournira "les performances du PC-like avec une faible consommation d'énergie".

Samsung avait déjà engagé à utiliser l'architecture big.LITTLE pour ses puces Exynos en 2013, et il est sûr de supposer que nous allons commencer à voir les nouvelles puces 14nm dans les appareils Samsung à un certain moment en 2013. Samsung a également publié un Kit processus de conception (PDK) pour ses clients afin qu'ils puissent commencer à concevoir les nouveaux modèles, les fichiers de la technologie , et des manuels de règles de conception sur la base des résultats de silicium à partir de copeaux de test de 14nm FinFET.

Milestone permet d'accélérer l'adoption de la technologie FinFET pour plus de puissance des systèmes efficaces et plus rapide sur les puces (SoC) s

Collaboration fournit la fondation pour la modélisation 3D et dispositif de soutien physique des règles de conception

Puce de test qualifie Souvenirs processus de FinFET et Synopsys® DesignWare® embarqués

Synopsys, Inc. (Nasdaq: SNPS), un leader mondial de la fourniture de logiciels, des services IP et utilisés pour accélérer l'innovation dans les puces et systèmes électroniques, a annoncé aujourd'hui que sa collaboration pluriannuel avec Samsung sur la technologie FinFET a franchi une étape cruciale: le succès tapeout de la première puce de test sur 14LPE le processus de Samsung. Alors que le processus FinFET offre une puissance importante et les avantages de performance par rapport au processus de plan traditionnel, le passage de transistors à deux dimensions à des transistors tridimensionnels introduit plusieurs nouveaux défis de l'outil IP et EDA telles que la modélisation. La collaboration pluriannuelle livré les technologies de modélisation fondamentaux pour l'extraction parasite 3D, la simulation de circuit et de support à la conception physique des appareils règle FinFET. Solution complète de Synopsys pour la mémoire embarquée, conception physique, extraction de parasites, l'analyse temporelle et signoff est construit sur cette base.

"Transistors FinFET peuvent livrer de plus faible consommation d'énergie et les performances du dispositif supérieur, mais ils apportent aussi des défis difficiles," a déclaré le Dr Choi Kyu-Myung, vice-président de Système LSI centre de conception de l'infrastructure, Device Solutions, Samsung Electronics. «Nous avons choisi Synopsys comme partenaire de collaboration de FinFET pour résoudre ces défis, en raison de notre histoire réussir ensemble à 20 nanomètres et d'autres nœuds. Nous continuons de mettre en commun notre expertise pour offrir des solutions innovantes FinFET."

FinFET prêt IP de Synopsys

Synopsys a travaillé en étroite collaboration avec Samsung pour développer une puce de test qui valide avancée processus de FinFET 14-nm de Samsung ainsi que Synopsys DesignWare embarqué Memories utilisant Synopsys Self-Test et réparation solution (STAR) Mémoire System®. La puce de test va permettre la corrélation des modèles de simulation pour le processus FinFET et contient des structures de test, les cellules standard, une PLL et SRAM embarqués. Les instances de mémoire comprennent SRAM à haute densité, conçus pour fonctionner à de très basses tensions et SRAM à haute vitesse pour valider la performance des processus.

Conception Synopsys FinFET-prêts Outils

Le passage du plan de transistors 3D à base de FinFET est un changement important qui nécessite une étroite collaboration technique entre les développeurs d'outils, les fonderies et les adopteurs précoces de fournir une solution forte. La technologie de modélisation très précise de Synopsys fournit la fondation pour le Galaxy ™ Plateforme de mise en œuvre de FinFET prêt. La plate-forme comprend IC Compiler ™ conception physique, la vérification physique IC Validator, StarRC ™ extraction de parasites, SiliconSmart caractérisation, CustomSim ™ et FineSim pour la simulation de FastSPICE, et la modélisation de l'appareil HSPICE® et la simulation de circuit.

"Samsung est un partenaire clé dans nos efforts et investissements pour développer une solution complète pour la technologie FinFET", a déclaré Antun Domic, vice-président senior et directeur général de Groupe de mise en œuvre de Synopsys. «La vaste collaboration de Synopsys avec Samsung nous permet d'offrir le meilleur de sa classe et les technologies IP pour aider les concepteurs à réaliser le plein potentiel de FinFET conceptions de transistors."